# PHENIKAA UNIVERSITY

## **Transistors FET**

Van Su Luong

#### **Contents**

The JFET JFET Characteristics and Parameters JFET Biasing The Ohmic Region The MOSFET MOSFET Characteristics and Parameters MOSFET Biasing The IGBT Troubleshooting Device Application

The Common-Source Amplifier The Common-Drain Amplifier The Common-Gate Amplifier The Class D Amplifier MOSFET Analog Switching MOSFET Digital Switching Troubleshooting Device Application

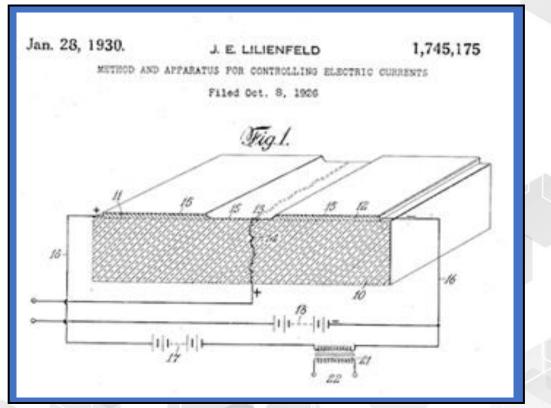

- The idea for a field-effect transistor (FET) was first proposed by Julius Lilienthal, a physicist and inventor. In 1930 he was granted a U.S. patent for the device.

- His ideas were later refined and developed into the FET. Materials were not available at the time to build his device. A practical FET was not constructed until the 1950's. Today FETs are the most widely used components in integrated circuits.

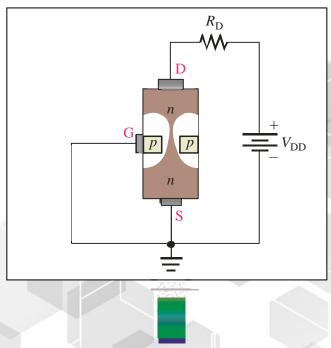

The JFET (or Junction Field Effect Transistor) is a normally ON device. For the *n*-channel device illustrated, when the drain is positive with respect to the source and there is no gate-source voltage, there is current in the channel.

When a negative gate voltage is applied to the FET, the electric field causes the channel to narrow, which in turn causes current to decrease.

UNIVERSITY

#### http://phenikaa-uni.<u>edu.vn</u>

As in the base of bipolar transistors, there are two types of JFETs: *n*-channel and *p*-channel. The dc voltages are opposite polarities for each type.

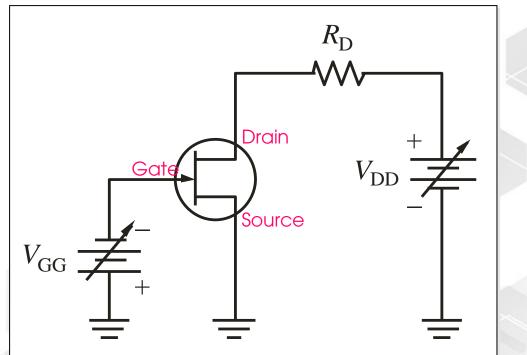

The symbol for an *n*-channel JFET is shown, along with the proper polarities of the applied dc voltages. For an *n*-channel device, the gate is always operated with a negative (or zero) voltage with respect to the source.

The JFET

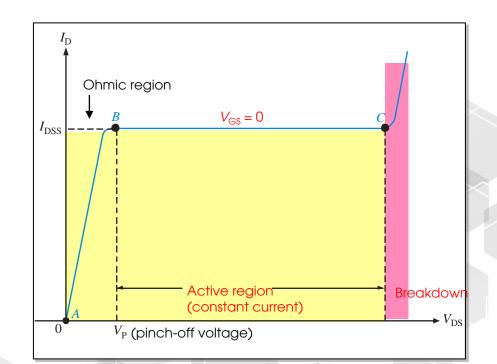

There are three regions in the characteristic curve for a JFET as illustrated for the case when  $V_{GS} = 0$  V.

Between A and B is the **Ohmic region**, where current and voltage are related by Ohm's law.

From *B* to *C* is the **active** (or *constant-current*) **region** where current is essentially independent of  $V_{\text{DS}}$ .

Beyond C is the **breakdown region**. Operation here can damage the FET.

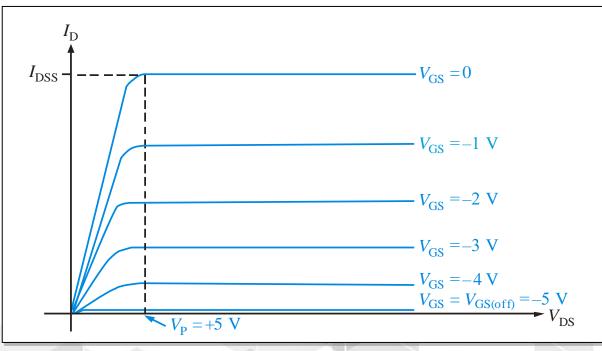

When  $V_{GS}$  is set to different values, the relationship between  $V_{DS}$  and  $I_D$  develops a family of characteristic curves for the device.

An *n*-channel characteristic is illustrated here. Notice that  $V_p$  is positive and has the same magnitude as  $V_{GS(off)}$ .

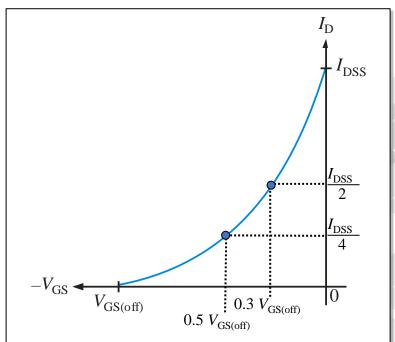

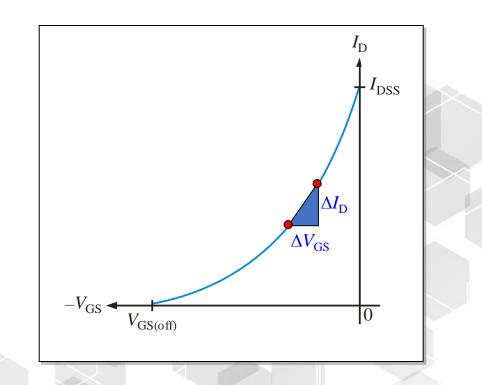

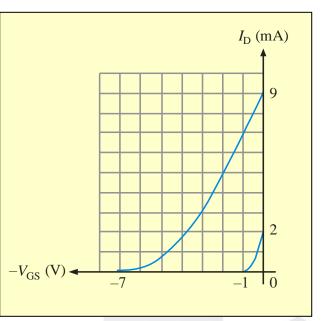

A plot of  $V_{GS}$  to  $I_D$  is called the transfer or transconductance curve. The transfer curve is a is a plot of the output current  $(I_D)$  to the input voltage  $(V_{GS})$ .

The transfer curve is based on the equation

$$I_{\rm D} = I_{\rm DSS} \left( 1 - \frac{V_{\rm GS}}{V_{\rm GS(off)}} \right)^2$$

By substitution, you can find other points on the curve for plotting the universal curve.

PHENIKAA UNIVERSITY

#### http://phenikaa-uni.edu.vn

### The **JFET**

**P**:

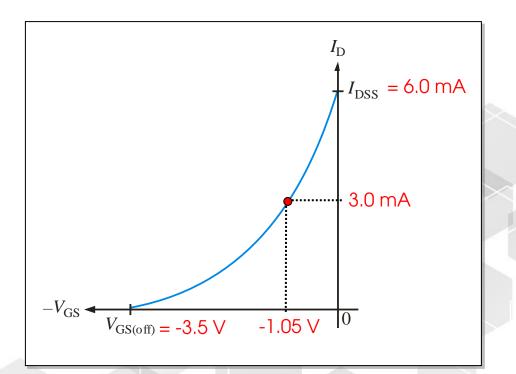

(a) Show the values of these end points on the transfer curve.

A certain 2N5458 JFET has  $I_{\text{DSS}} = 6.0$  mA and  $V_{\text{GS(off)}} = -3.5$  V.

(b) Show the point for the case when  $I_D = 3.0$  mA.

## Solution:

(b) When  $I_{\rm D} = I_{\rm DSS}$ ,  $V_{\rm GS} = 0.3$  $V_{\rm GS(off)}$ . Therefore,  $V_{\rm GS} = -1.05$  V

PHENIKAA UNIVERSITY

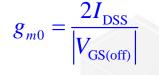

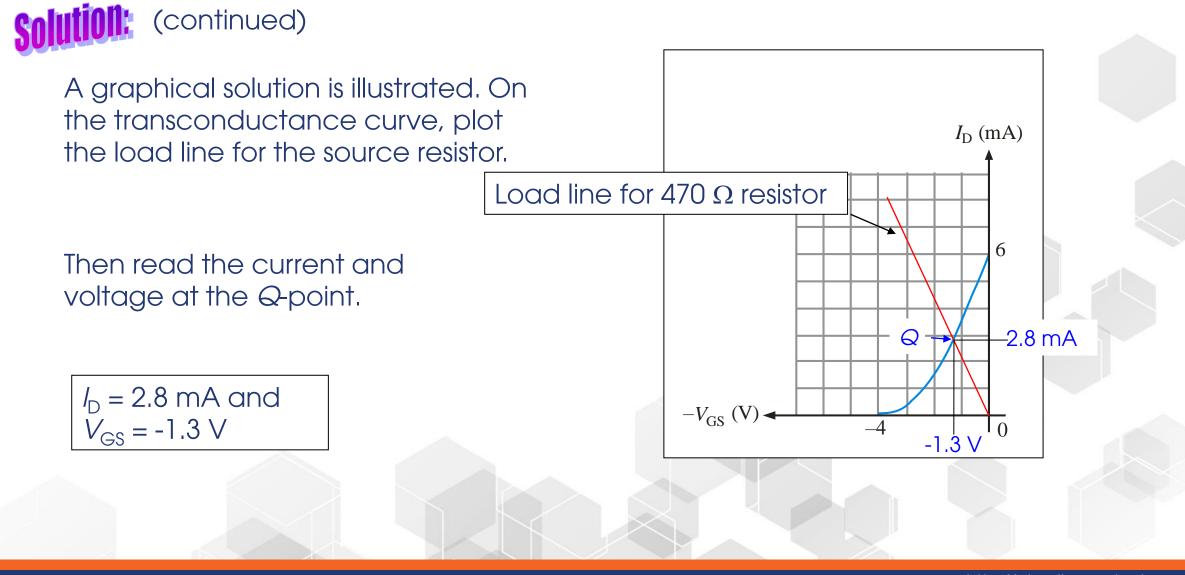

The transconductance is the ratio of a change in output current ( $DI_D$ ) to a change in the input voltage ( $DV_{GS}$ ).

This definition is  $g_m = \frac{\Delta I_D}{\Delta V_{GS}}$

The following approximate formula is useful for calculating gm if you know  $g_{m_0}$ .

$$g_m = g_{\rm m0} \left( 1 - \frac{V_{\rm GS}}{V_{\rm GS(off)}} \right)$$

The value of  $g_{m0}$  can be found from

Because the slope changes at every point along the curve, the transconductance is not constant, but depends on where it is measured.

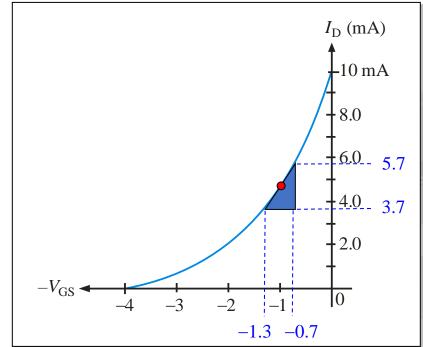

Example:

What is the transconductance for the JFET at the point shown?

$$g_{m} = \frac{\Delta I_{\rm D}}{\Delta V_{\rm GS}} = \frac{5.7 \text{ mA} - 3.7 \text{ mA}}{-0.7 \text{ V} - (-1.3 \text{ V})}$$

$$= \frac{2.0 \text{ mA}}{0.6 \text{ V}} = 3.33 \text{ mS}$$

#### **JFET Input Resistance**

The input resistance of a JFET is given by:  $R_{IN} = \frac{V_{GS}}{I_{CSS}}$

where  $I_{GSS}$  is the current into the reverse biased gate.

JFETs have very high input resistance, but it drops when the temperature increases.

Compare the input resistance of a 2N5485 at 25 °C and at 100 °C. The specification sheet shows that for  $V_{GS} = -20$  V,  $I_{GSS} - 1$  nA at 25 °C and 0.2 mA at 100 °C.

At 25 °C,

$$R_{IN} = \left| \frac{V_{GS}}{I_{GSS}} \right| = \left| \frac{20 \text{ V}}{1 \text{ nA}} \right| = 20 \text{ G}\Omega!$$

At 100 °C,  $R_{IN} = \left| \frac{V_{GS}}{I_{GSS}} \right| = \left| \frac{20 \text{ V}}{0.2 \text{ }\mu\text{A}} \right| = 100 \text{ M}\Omega$

#### **JFET Biasing**

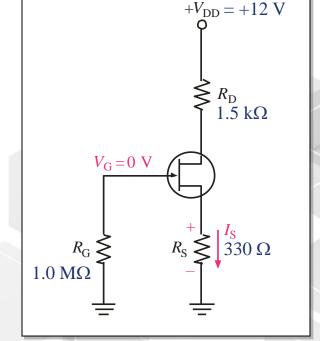

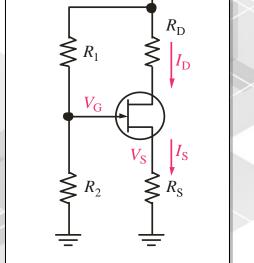

Self-bias is simple and effective, so it is the most common biasing method for JFETs. With self bias, the gate is essentially at 0 V.

An *n*-channel JFET is illustrated. The current in  $R_{\rm S}$  develops the necessary reverse bias that forces the gate to be less than the source.

### Example:

Assume the resistors are as shown and the drain current is 3.0 mA. What is  $V_{GS}$ ?

### Solution:

$V_{\rm G}$  = 0 V;  $V_{\rm S}$  = (3.0 mA)(330 W) = 0.99 V  $V_{\rm GS}$  = 0 - 0.99 V = - 0.99 V

#### http://phenikaa-uni.edu.vn

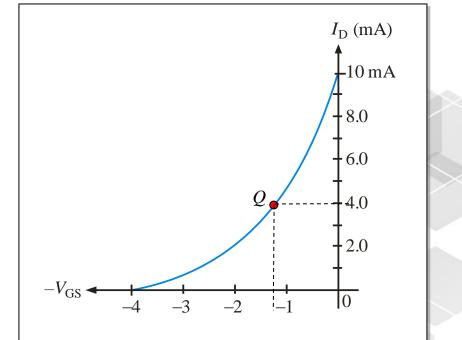

You can use the transfer curve to obtain a reasonable value for the source resistor in a self-biased circuit.

#### **Example**:

**JFET Biasing**

What value of  $R_s$  should you use to set the Q point as shown?

#### Solution:

The Q point is approximately at  $I_D$  = 4.0 mA and  $V_{GS}$  = -1.25 V.

$$R_{\rm S} = \left| \frac{V_{\rm GS}}{I_{\rm D}} \right| = \frac{1.25 \text{ V}}{3.0 \text{ mA}} = 375 \Omega$$

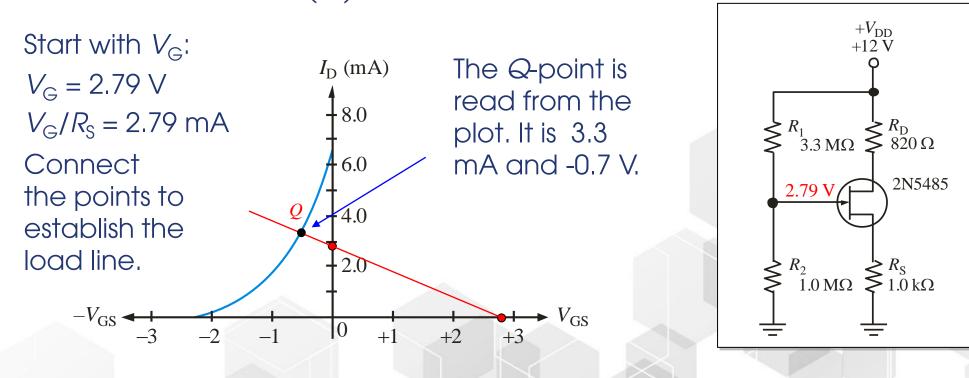

Voltage-divider biasing is a combination of a voltage-divider and a source resistor to keep the source more positive than the gate.

$V_{\rm G}$  is set by the voltage-divider and is independent of  $V_{\rm S}$ .  $V_{\rm S}$  must be larger than  $V_{\rm G}$  in order to maintain the gate at a negative voltage with respect to the source.

Voltage-divider bias helps stabilize the bias for variations between transistors.

**JFET Biasing**

$+V_{\rm DD}$

#### **JFET Biasing**

A graphical analysis of voltage-divider biasing is illustrated. A typical transconductance curve for the 2N5485 is shown with  $I_{DSS}$  = 6.5 mA and  $V_{GS(off)}$  = -2.2 V.

#### http://phenikaa-uni.<u>edu.vn</u>

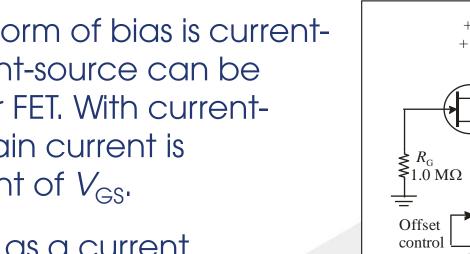

An even more stable form of bias is currentsource bias. The current-source can be either a BJT or another FET. With currentsource biasing, the drain current is essentially independent of  $V_{GS}$ .

In this circuit  $Q_2$  serves as a current source for  $Q_1$ . An advantage to this particular circuit is that the output can be adjusted (using  $R_{s_2}$ ) for 0 V DC.

$+V_{\rm DD}$ +15 V

2N5458

$\underset{470}{\overset{8}{\underset{}}} R_{s_1}$

$1.0 \text{ k}\Omega$

$\geq R_{S3}$  $\sum_{n=1}^{\infty} k\Omega$

-15 V

2N5458

$V_{out}$

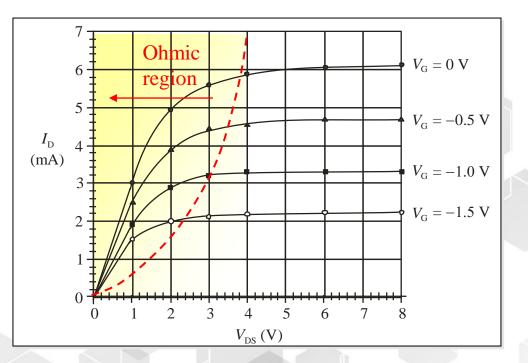

### **JFET Ohmic Region**

As described before, the ohmic region is between the origin and the active region. A JFET operated in this region can act as a variable resistor.

Data from an actual FET is shown. The slopes (which represent conductance) of successive  $V_{GS}$  lines are different in the ohmic region. This difference is exploited for use as a voltage controlled resistance.

### **JFET Ohmic Region**

PHENIKAA UNIVERSITY

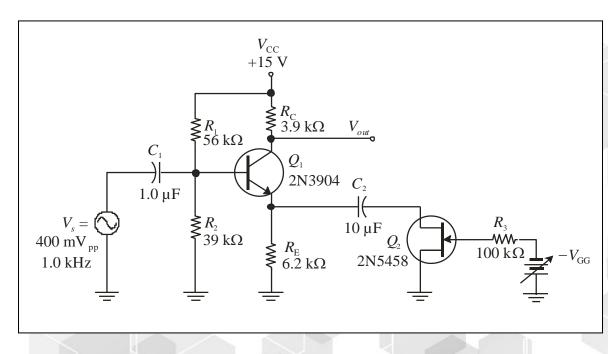

Here is a circuit in which the JFET is used as a variable resistor. Notice that that the drain is connected through a capacitor, which means the JFET's *Q*-point is at the origin.

The gain of the BJT depends on the dc voltage setting of  $V_{GG}$ .

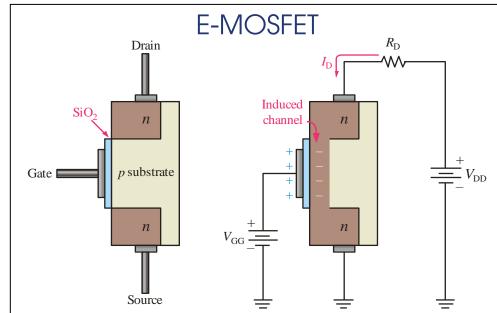

The metal oxide semiconductor FET uses an insulated gate to isolate the gate from the channel. Two types are the enhancement mode (E-MOSFET) and the depletion mode (D-MOSFET).

An E-MOSFET has no channel until it is induced by a voltage applied to the gate, so it operates only in enhancement mode. An *n*-channel type is illustrated here; a positive gate voltage induces the channel.

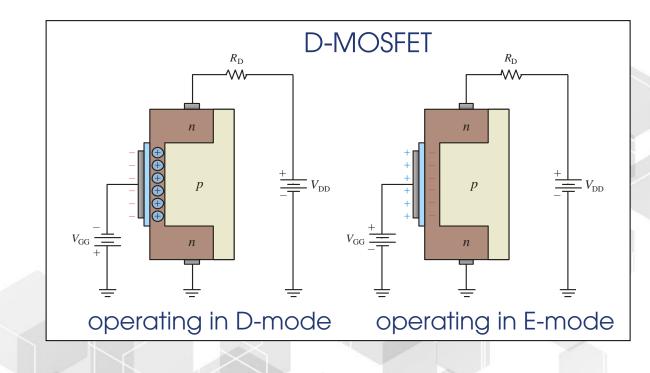

The D-MOSFET has a channel that can is controlled by the gate voltage. For an *n*-channel type, a negative voltage depletes the channel; and a positive voltage enhances the channel.

A D-MOSFET can operate in either mode, depending on the gate voltage.

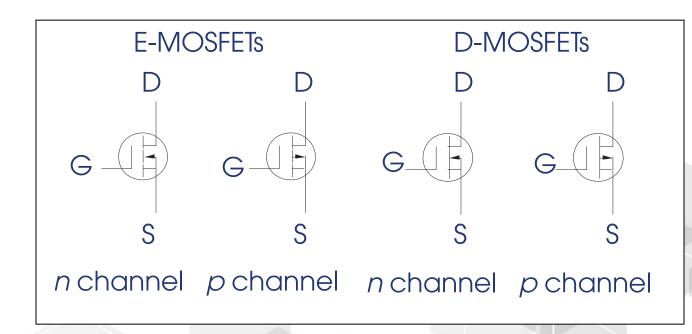

MOSFET symbols are shown. Notice the broken line representing the E-MOSFET that has an induced channel. The *n* channel has an induced channel. The *n* channel has an induced pointing arrow.

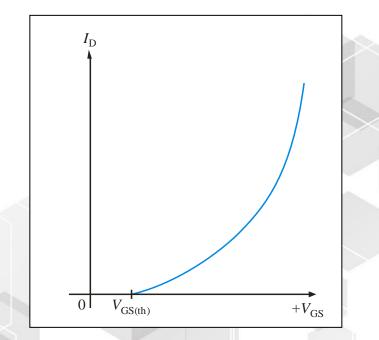

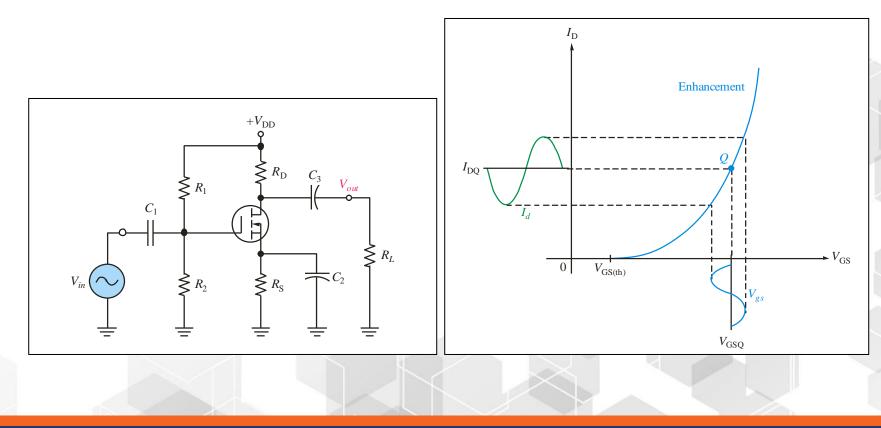

The transfer curve for a MOSFET is has the same parabolic shape as the JFET but the position is shifted along the *x*-axis. The transfer curve for an *n*-channel E-MOSFET is entirely in the first quadrant as shown.

The curve starts at  $V_{GS(th)}$ , which is a nonzero voltage that is required to have channel conduction. The equation for the drain current is

$$I_{\rm D} = K \left( V_{\rm GS} - V_{\rm GS(th)} \right)^2$$

UNIVERSIT

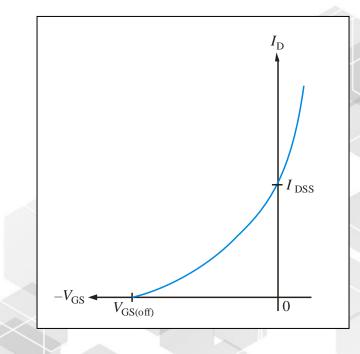

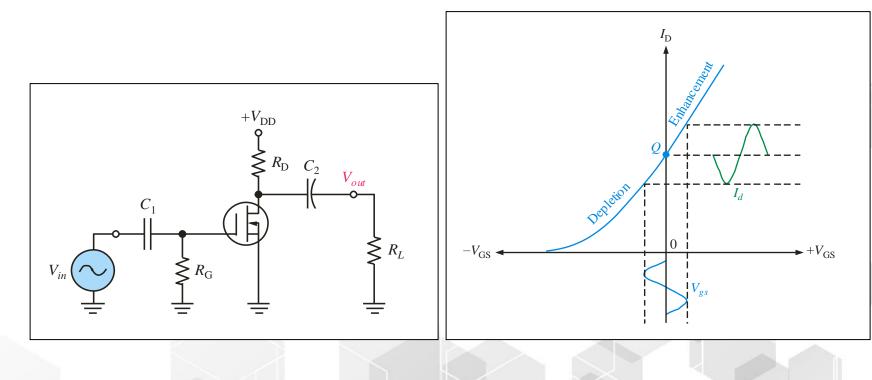

Recall that the D-MOSFET can be operated in either mode. For the *n*-channel device illustrated, operation to the left of the *y*axis means it is in depletion mode; operation to the right means is in enhancement mode.

As with the JFET,  $I_D$  is zero at  $V_{GS(off)}$ . When VGS is 0, the drain current is  $I_{DSS}$ , which for this device is *not* the maximum current. The equation for drain current is

$$I_{\rm D} \cong I_{\rm DSS} \left( 1 - \frac{V_{\rm GS}}{V_{\rm GS(off)}} \right)^2$$

#### **MOSFET Biasing**

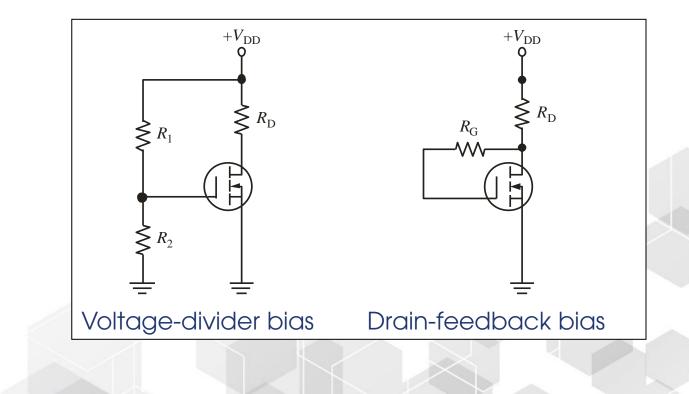

E-MOSFETs can be biased using bias methods like the BJT methods studied earlier. Voltage-divider bias and drain-feedback bias are illustrated for *n*-channel devices.

#### **MOSFET Biasing**

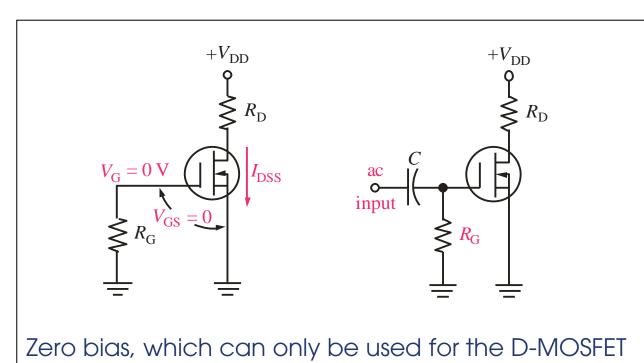

The simplest way to bias a D-MOSFET is with zero bias. This works because the device can operate in either depletion or enhancement mode, so the gate can go above or below 0 V.

# FET Amplifiers and Switching Circuits

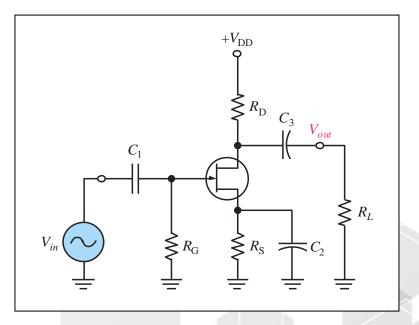

In a CS amplifier, the input signal is applied to the gate and the output signal is taken from the drain. The amplifier has higher input resistance and lower gain than the equivalent CE amplifier.

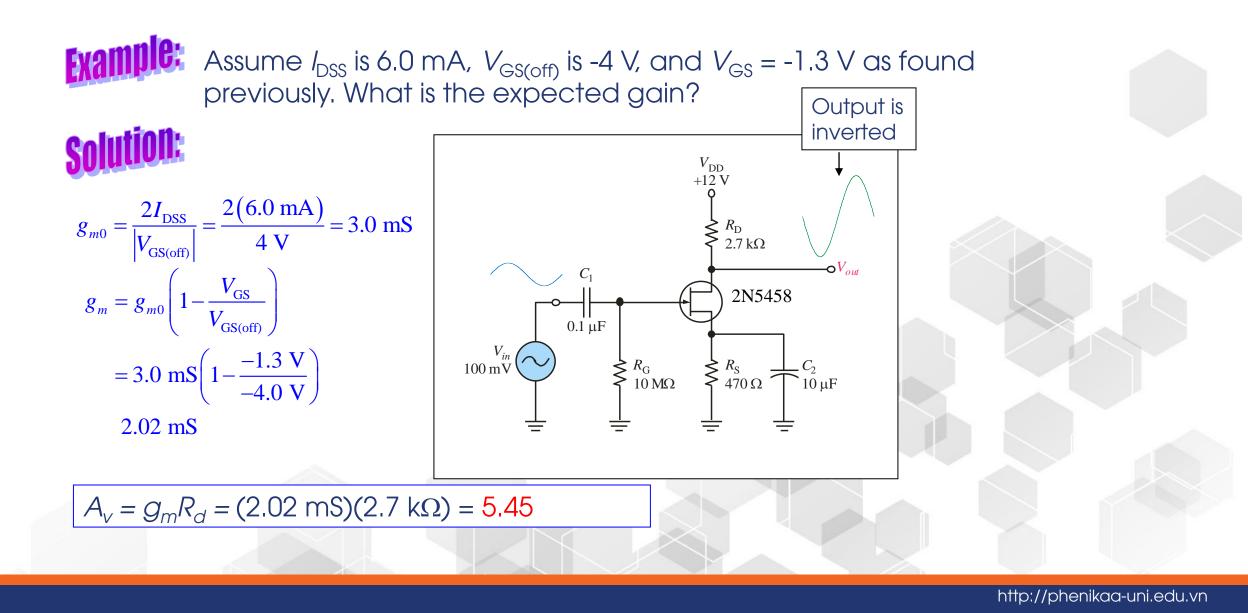

The voltage gain is given by the equation  $A_v = g_m R_{d'}$

Recall that conductance is the reciprocal of resistance and admittance is the reciprocal of impedance. Data sheets typically specify the forward transfer admittance,  $y_{fs}$  rather than transconductance,  $g_m$ . The definition of  $y_{fs}$  is  $M_{rs}$

$$y_{fs} = \frac{\Delta I_{\rm D}}{\Delta V_{\rm G}}$$

| DYNAMIC CHARACTERISTICS                                           |                  | Symbol          | Min          | Тур          | Max          | Unit       |

|-------------------------------------------------------------------|------------------|-----------------|--------------|--------------|--------------|------------|

| Forward Transfer Admittance<br>( $V_{DS}$ = 15 Vdc, $V_{GS}$ = 0) | 2N5457<br>2N5458 | Y <sub>fs</sub> | 1000<br>1500 | 3000<br>4000 | 5000<br>5500 | $\mu$ mhos |

An alternate gain expression for a CS amplifier is  $A_v = y_{fs}R_{d'}$

You can estimate what the transfer characteristic looks like from values on the specification sheet, but keep in mind that large variations are common with JFETs. For example, the range of specified values for a 2N5458 is shown.

| OFF CHARACTERISTICS                                                 |                  | Symbol        | Min          | Тур | Max          | Unit |

|---------------------------------------------------------------------|------------------|---------------|--------------|-----|--------------|------|

| Gate-Source Cutoff Voltage<br>( $V_{DS}$ = 15 Vdc, $i_D$ = 10 nAdc) | 2N5457<br>2N5458 | $V_{GS(off)}$ | -0.5<br>-1.0 | -   | -6.0<br>-7.0 | Vdc  |

|                                                                     |                  |               |              |     |              |      |

| ON CHARACTERISTICS                                                  |                  | Symbol        | Min          | Тур | Max          | Uni  |

http://phenikaa-uni.edu.vn

#### http://phenikaa-uni.edu.vn

#### **The Common-Source Amplifier**

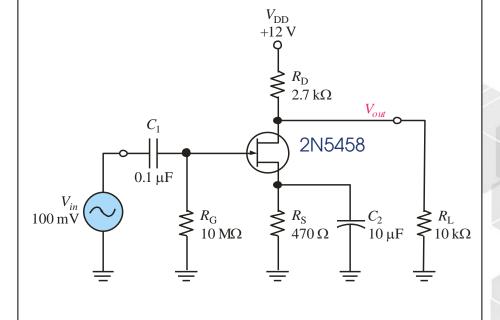

To analyze the CS amplifier. you need to start with dc values. It is useful to estimate  $I_D$  based on typical values; specific circuits will vary from this estimate.

### Example:

For a typical 2N5458, what is the drain current?

From the specification sheet, the typical  $I_{DSS} = 6.0$  mA and  $V_{GS(off)} = -4$  V. These values can be plotted along with the load line to obtain a graphical solution.

$V_{DD}$  +12 V  $R_{D}$   $2.7 k\Omega$   $V_{out}$   $V_{in}$   $V_$

**Solution:** (continued)

Alternatively, you can obtain  $I_{\rm D}$  using Equation 9-2:  $I_{\rm D} = I_{\rm DSS} \left( 1 - \frac{I_{\rm D} R_{\rm S}}{V_{\rm CSC(6)}} \right)$

The solution to this quadratic equation is simplified using a calculator that can handle quadratic equations.

After entering the equation, enter the known values, but leave  $I_D$  open. For the typical values for the 2N5458,  $(I_{DSS} = 6 \text{ mA} \text{ and } V_{GS(off)} = -4 \text{ V})$  with a source resistance of 470  $\Omega$ , we find 2.75 mA. ID=IDSS\*(1-(-ID\*RS/VG... ID= .0027494671581759 IDSS=.006 RS= 470 VGSOFF= 4.0 bound=(-1E99,1E99) GRAPH RANGE ZOOM TRACE SOLVE

#### http://phenikaa-uni.edu.vn

#### **The Common-Source Amplifier**

The gain is reduced when a load is connected to the amplifier because the total ac drain resistance ( $R_d$ ) is reduced.

Example:

How does the addition of the 10 k $\Omega$  load affect the gain?

Solution:

$R_{d} = \frac{R_{\rm D}R_{\rm L}}{R_{\rm D} + R_{\rm L}}$  $= \frac{(2.7 \text{ k}\Omega)(10 \text{ k}\Omega)}{2.7 \text{ k}\Omega + 10 \text{ k}\Omega}$  $= 2.13 \text{ k}\Omega$

$A_v = g_m R_d = (2.02 \text{ mS})(2.13 \text{ k}\Omega) = 4.29$

In operation, the D-MOSFET has the unique property in that it can be operated with zero bias, allowing the signal to swing above and below ground. This means that it can operate in either D-mode or E-mode.

UNIVERSITY

The E-MOSFET is a normally off device. The *n*-channel device is biased on by making the gate positive with respect to the source. A voltagedivider biased E-MOSFET amplifier is shown.

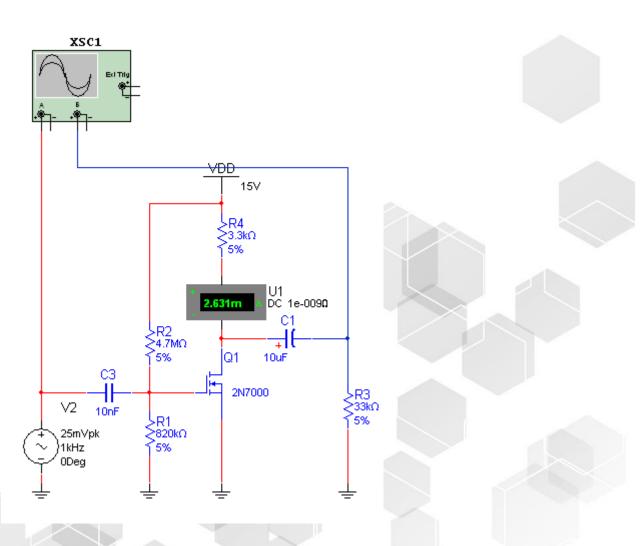

The E-MOSFET amplifier in Example 9-8 is illustrated in Multisim using a 2N7000 MOSFET.

#### http://phenikaa-uni.edu.vn

**The Common-Drain Amplifier**

In a CD amplifier, the input signal is applied to the gate and the output signal is taken from the source. There is no drain resistor, because it is *common* to the input and output signals.

The voltage gain is given by the equation

The voltage gain is always < 1, but the power gain is not.

$$=\frac{g_m R_s}{1+g_m R_s}$$

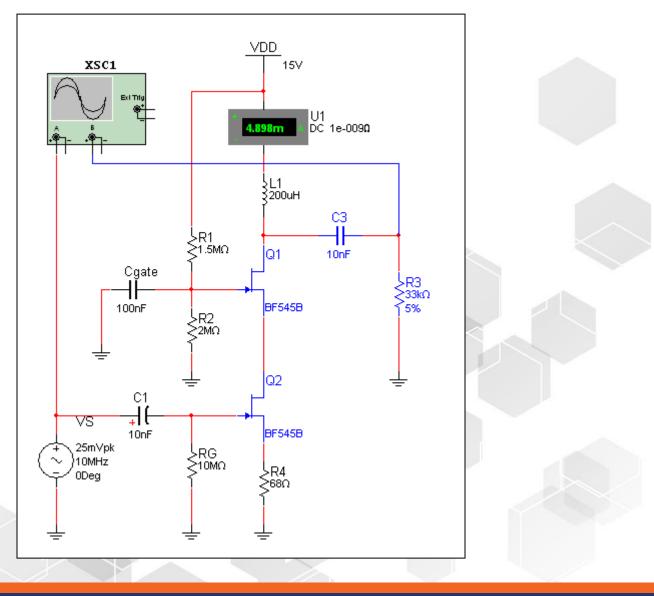

#### **The Cascode Amplifier**

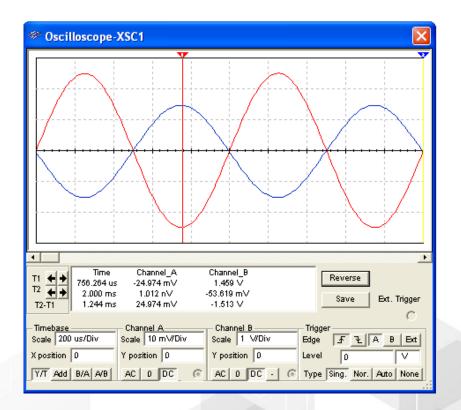

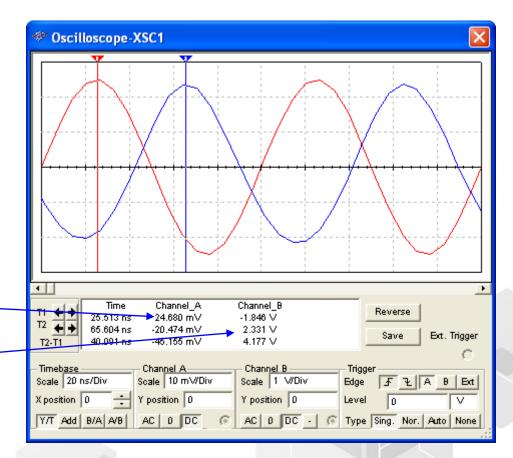

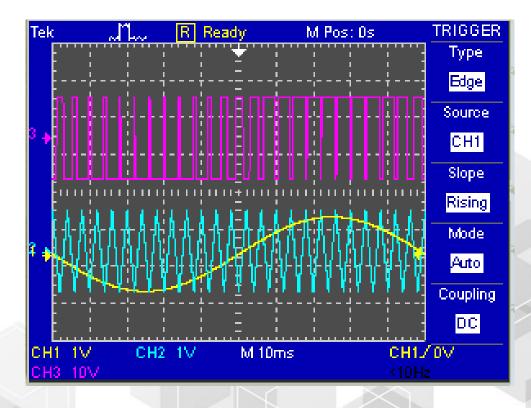

The cascode connection is a combination of CS and CG amplifiers. This forms a good high-frequency amplifier. The input and output signals at 10 MHz are shown for this circuit on the following slide...

#### **The Cascode Amplifier**

### Example:

The input signal for the cascode amplifier is shown in red; the output is blue. What is the gain?

The peak of the input is 24.7 mV. The peak of the output is 2.33 V.

$A_V = 94.3$

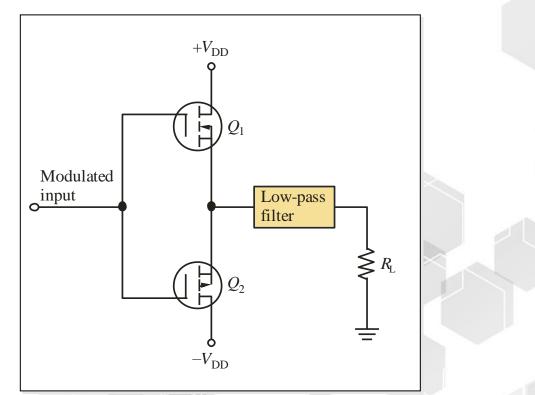

MOSFETs are useful as class-D amplifiers, which are very efficient because they operate as switching amplifiers. They use pulse width modulation, a process in which the input signal is converted to a series of pulses. The pulse width varies proportionally to the amplitude of the input signal.

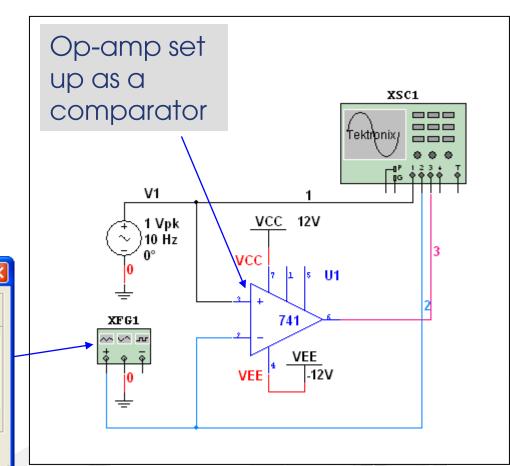

Pulse-width modulation is easy to set up in Multisim. The following slide shows the circuit. A sine wave is compared to a faster triangle wave of the about the same amplitude using a comparator (a 741 op-amp can be used at low frequencies).

A circuit that you can use in lab or in Multisim to observe pulse width modulation in action. The scope display is shown on the following slide...

Waveforms

Signal Options Frequency

Duty Cycle

Amplitude

Offset

250

50

1.1

Set Rise/Fall Time

Common

$(\mathbf{G})$

0

÷ \/

Hz

×.

V.

C

The signal is the yellow sine wave and is compared repeatedly to the triangle (cyan). The result of the comparison is the output (magenta).

The modulated signal is amplified by class-B complementary MOSFET transistors. The output is filtered by a low-pass filter to recover the original signal and remove the higher modulation frequency.

PWM is also useful in control applications such as motor controllers. MOSFETs are widely used in these applications because of fast switching time and low on-state resistance.

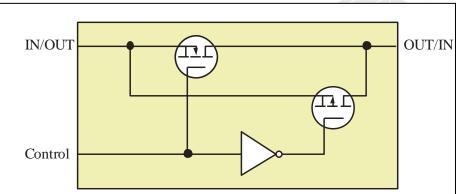

#### **The Analog Switch**

MOSFETs are also used as analog switches to connect or disconnect an analog signal. Analog switches are available in IC form – for example the CD4066 is a quad analog switch that used parallel *n*and *p*-channel MOSFETs. The configuration shown allows signals to be passed in either direction.

Advantages of MOSFETs are that they have relatively low on-state resistance and they can be used at high frequencies, such as found in video applications.

Simplified internal construction of a bidirectional IC analog switch.