# PHENIKAA UNIVERSITY

# **The Operational Amplifier**

Van Su Luong

#### **Contents**

- Introduction to Operational Amplifiers

- Op-Amp Input Modes and Parameters

- Negative Feedback

- Op-Amps with Negative Feedback

- Effects of Negative Feedback on Op-Amp

Impedances

- Bias Current and Offset Voltage

- Open-Loop Frequency and Phase Responses

- Closed-Loop Frequency Response

- Troubleshooting

- Comparators

- Summing Amplifiers

- Integrators and Differentiators

- Troubleshooting

Device Application

- Programmable Analog Technology

#### http://phenikaa-uni.edu.vn

#### **Operational Amplifers**

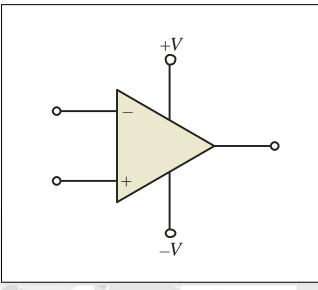

# **Operational amplifiers (op-amps)** are very high gain dc coupled amplifiers with differential inputs. One of the inputs is called the inverting input (-); the other is called the noninverting input. Usually there is a single output.

Most op-amps operate from plus and minus supply voltages, which may or may not be shown on the schematic symbol.

#### **The Ideal Op-Amp**

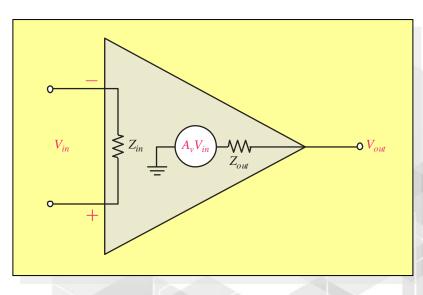

The ideal op-amp has characteristics that simplify analysis of op-amp circuits. Ideally, op-amps have *infinite voltage gain, infinite bandwidth,* and *infinite input impedance*. In addition, the ideal op-amp has *zero output impedance*.

#### **The Practical Op-Amp**

Practical op-amps have characteristics that often can be treated as ideal for certain situations but can never actually attain ideal characteristics. In addition to finite gain, bandwidth, and input impedance, they have other limitations.

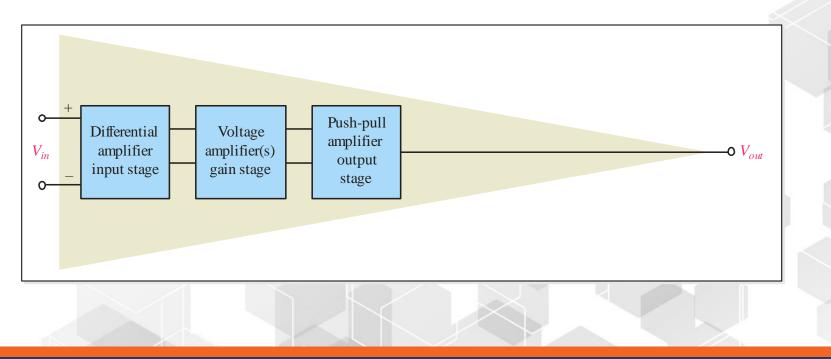

## **Block Diagram**

Internally, the typical op-amp has a differential input, a voltage amplifier, and a push-pull output. Recall from the discussion in previous Section of the text that the differential amplifier amplifies the *difference* in the two inputs.

#### **Signal modes**

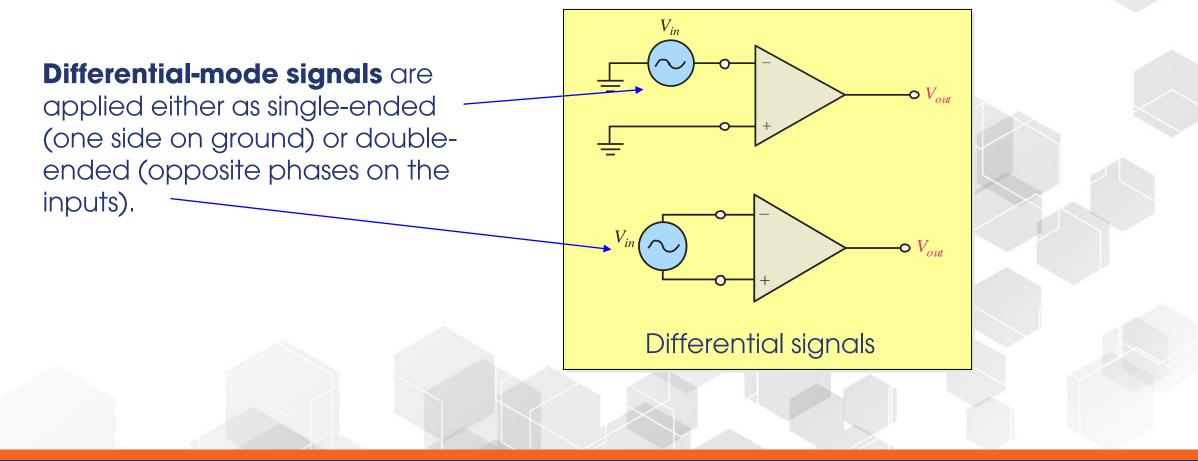

The input signal can be applied to an op-amp in differential-mode or in common-mode.

## Signal modes

The input signal can be applied to an op-amp in differential-mode or in common-mode.

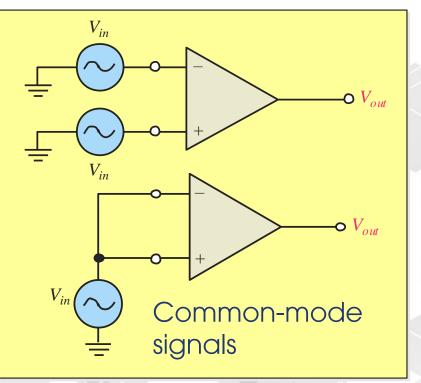

#### Common-mode signals are

applied to both sides with the same phase on both.

Usually, common-mode signals are from unwanted sources, and affect both inputs in the same way. The result is that they are essentially cancelled at the output.

#### **Common-Mode Rejection Ratio**

The ability of an amplifier to amplify differential signals and reject common-mode signals is called the **common-mode rejection ratio (CMRR)**.

CMRR is defined as  $CMRR = \frac{A_{ol}}{A_{or}}$

where  $A_{ol}$  is the open-loop differential-gain and  $A_{cm}$  is the common-mode gain.

CMRR can also be expressed in decibels as  $CMRR = 20 \log \left( \frac{A_{ol}}{A} \right)$

## **Common-Mode Rejection Ratio**

#### Example:

What is CMRR in decibels for a typical 741C op-amp?

The typical open-loop differential gain for the 741C is 200,000 and the typical common-mode gain is 6.3.

Solution:

$$CMRR = 20 \log \left(\frac{A_{ol}}{A_{cm}}\right)$$

$$= 20 \log \frac{200,000}{6.3} = 90 \text{ dB}$$

(The minimum specified CMRR is 70 dB.)

### **Voltage and Current Parameters**

$V_{O(p-p)}$ : The **maximum output voltage swing** is determined by the op-amp and the power supply voltages

$V_{OS}$ : The **input offset voltage** is the differential dc voltage required between the inputs to force the output to zero volts.

*I*<sub>BIAS</sub>: The **input bias current** is the average of the two dc currents required to bias the differential amplifier

*I*<sub>OS</sub>: The **input offset current** is the difference between the two dc bias currents

#### http://phenikaa-uni.edu.vn

#### **Impedance Parameters**

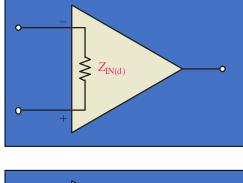

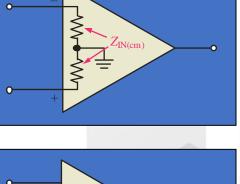

$Z_{IN(d)}$ : The differential input **impedance** is the total resistance between the inputs

$Z_{IN(cm)}$ : The **common-mode input impedance** is the resistance between each input and ground

$Z_{out}$ : The output impedance is the resistance viewed from the output of the circuit.

#### http://phenikaa-uni.edu.vn

#### **Other Parameters**

Slew rate: The **slew rate** is the maximum rate of change of the output voltage in response to a step input voltage

Slew Rate =  $\frac{\Delta V_{out}}{\Delta V_{out}}$

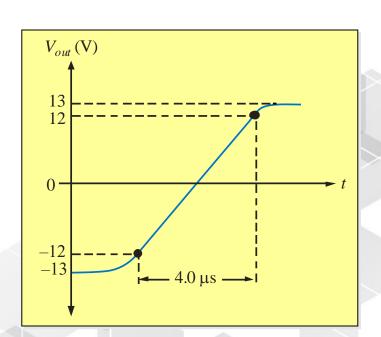

Determine the slew rate for the output response to a step input.

Slew Rate =  $\frac{\Delta V_{out}}{\Delta t} = \frac{(+12 \text{ V}) - (-12 \text{ V})}{4.0 \text{ }\mu\text{s}}$ = 6 V/ms

#### **Negative Feedback**

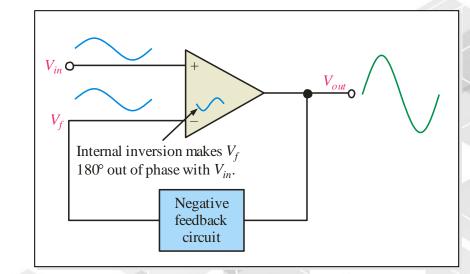

**Negative feedback** is the process of returning a portion of the output signal to the input with a phase angle that opposes the input signal.

The advantage of negative feedback is that precise values of amplifier gain can be set. In addition, bandwidth and input and output impedances can be controlled.

UNIVERSIT

$\circ V_{out}$

Feedback

circuit

#### **Noninverting Amplifier**

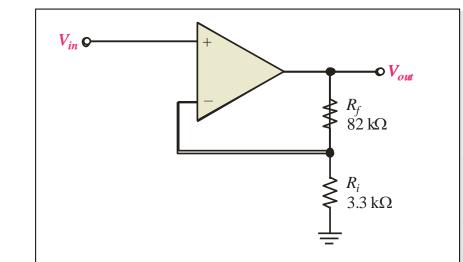

A **noninverting amplifier** is a configuration in which the signal is on the noninverting input and a portion of the output is returned to the inverting input.

Vin

Feedback forces  $V_f$  to be equal to  $V_{in}$ , hence  $V_{in}$  is across  $R_i$ . With basic algebra, you can show that the closed-loop gain of the noninverting amplifier is

$A_{cl(\mathrm{NI})} = 1 + \frac{R_f}{R_f}$

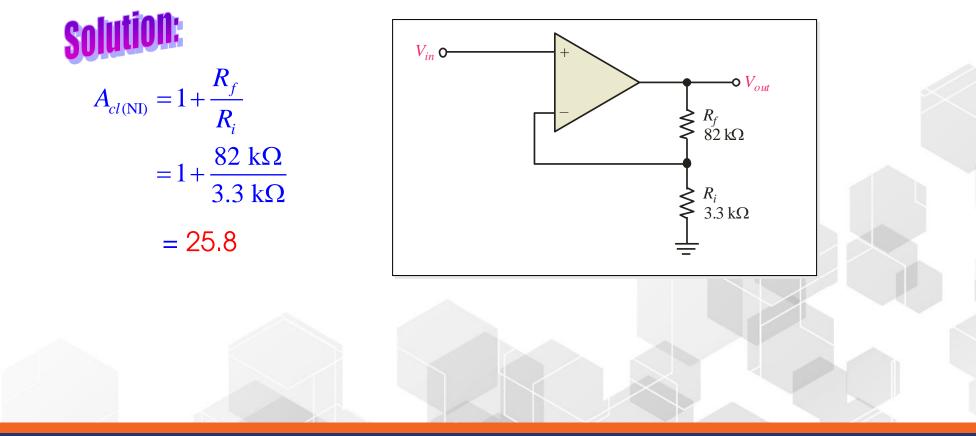

## **Noninverting Amplifier**

#### Example:

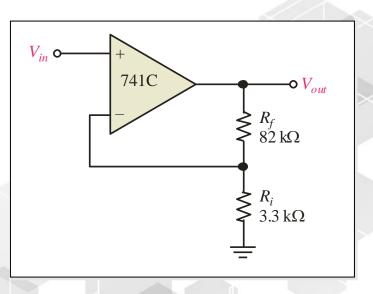

Determine the gain of the noninverting amplifier shown.

### **Noninverting Amplifier**

A special case of the inverting amplifier is when  $R_f = 0$  and  $R_i = \infty$ . This forms a voltage follower or unity gain buffer with a gain of 1.

The input impedance of the voltage follower is very high, producing an excellent circuit for isolating one circuit from another, which avoids "loading" effects.

#### **Inverting Amplifier**

An **inverting amplifier** is a configuration in which the noninverting input is grounded and the signal is applied through a resistor to the inverting input.

Feedback forces the inputs to be nearly identical; hence the inverting input is very close to 0 V. The closed-loop gain of the inverting amplifier is

$A_{cl(I)} = -\frac{R_f}{R}$

$V_{in} = V_{out}$   $V_{out}$   $V_{out}$   $V_{out}$   $V_{out}$

$R_i$

$R_f$

᠕᠕ᡔ

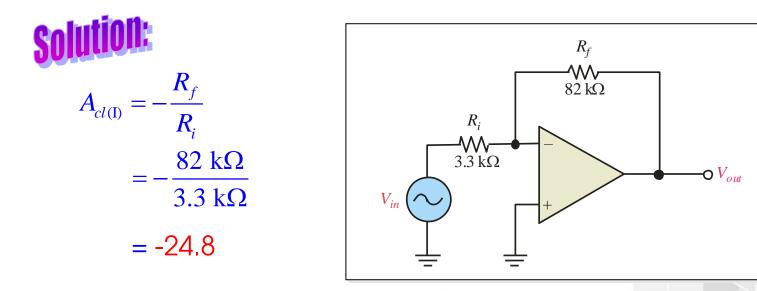

## **Inverting Amplifier**

## Example:

Determine the gain of the inverting amplifier shown.

The minus sign indicates inversion.

http://phenikaa-uni.edu.vn

#### Impedances

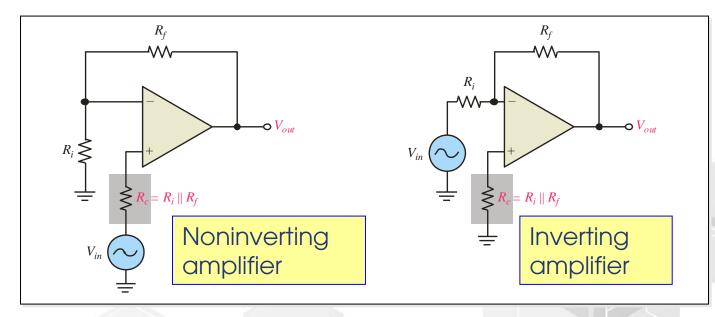

Noninverting amplifier:

$Z_{out(NI)} = \frac{Z_{out}}{(1 + A_{ol}B)}$

$Z_{in(NI)} = (1 + A_{ol}B)Z_{in}$  Generally, assumed to be  $\infty$ Generally, assumed to be 0

Note that the output impedance has the same form for both amplifiers.

http://phenikaa-uni.edu.vn

#### **Bias Current Compensation**

For op-amps with a BJT input stage, bias current can create a small output error voltage. To compensate for this, a resistor equal to  $R_i | R_f$  is added to one of the inputs.

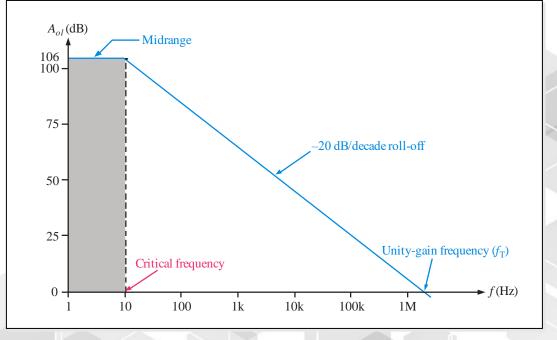

#### **Bandwidth Limitations**

Many op-amps have a roll off rate determined by a single low-pass *RC* circuit, giving a constant -20 dB/decade down to unity gain.

Op-amps with this characteristic are called *compensated* op-amps. The blue line represents the open-loop frequency characteristic (Bode plot) for the opamp.

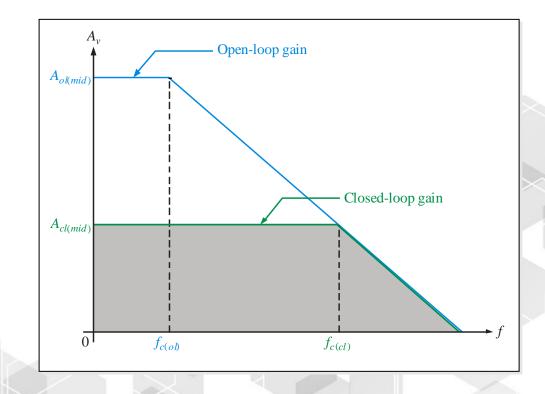

#### **Bandwidth Limitations**

For op-amps with a -20 dB/decade open-loop gain, the closed-loop critical frequency is given by  $f_{c(cl)} = f_{c(ol)}(1 + BA_{ol(mid)})$

The closed-loop critical frequency is higher than the open-loop critical frequency by the factor (1 +  $BA_{ol(mid)}$ ). This means that you can achieve a higher BW by accepting less gain. For a compensated opamp,  $A_{cl} f_{(cl)} = A_{ol} f_{c(ol)}$ .

#### **Bandwidth Limitations**

The equation,  $A_{cl} f_{(cl)} = A_{ol} f_{c(ol)}$  shows that the product of the gain and bandwidth are constant. The gain-bandwidth product is also equal to the unity gain frequency. That is  $f_T = A_{cl} f_{c(cl)}$ , where  $f_T$  is the unity-gain bandwidth.

**Example:** The  $f_T$  for a 741C op amp is 1 MHz. What is the  $BW_{cl}$  for the amplifier? **Solution:**   $A_{cl(NI)} = 1 + \frac{R_f}{R_i} = 1 + \frac{82 \text{ k}\Omega}{3.3 \text{ k}\Omega} = 25.8$  $BW_{cl} = \frac{f_T}{A_{cl}} = \frac{1 \text{ MHz}}{25.8} = 38.8 \text{ kHz}$

# **Basic Op-Amp Circuits**

#### **Comparators**

PHENIKAA UNIVERSITY

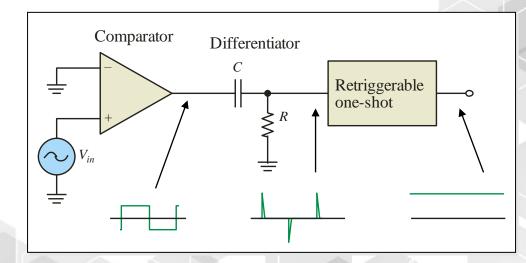

A **comparator** is a specialized nonlinear op-amp circuit that compares two input voltages and produces an output state that indicates which one is greater. Comparators are designed to be fast and frequently have other capabilities to optimize the comparison function.

An example of a comparator application is shown. The circuit detects a power failure in order to take an action to save data. As long as the comparator senses  $V_{in}$ , the output will be a dc level.

#### http://phenikaa-uni.edu.vn

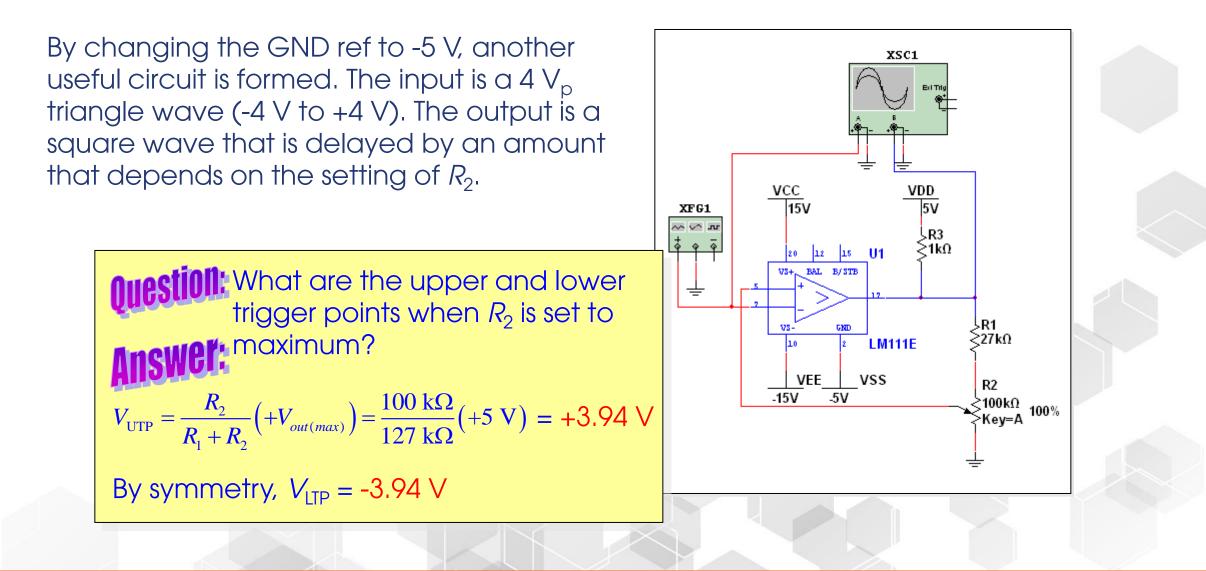

**Comparator with Hysteresis**

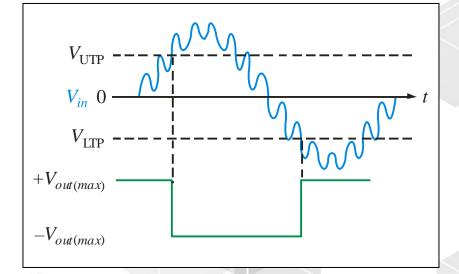

Sometimes the input signal to a comparator may vary due to noise superimposed on the input. The result can be an unstable output. To avoid this, hysteresis can be used.

Hysteresis is incorporated by adding regenerative (positive) feedback, which creates two switching points: the upper trigger point (UTP) and the lower trigger point (LTP). After one trigger point is crossed, it becomes inactive and the other one becomes active.

#### http://phenikaa-uni.edu.vn

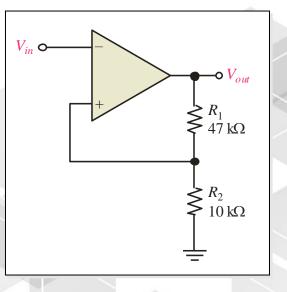

#### **Comparator with Hysteresis**

A comparator with hysteresis is also called a **Schmitt trigger**. The trigger points are found by applying the voltage-divider rule:

$$V_{\text{UTP}} = \frac{R_2}{R_1 + R_2} \left( + V_{out(max)} \right) \quad \text{and} \quad V_{\text{LTP}} = \frac{R_2}{R_1 + R_2} \left( -V_{out(max)} \right)$$

What are the trigger points for the circuit if the maximum output is  $\pm 13$  V?

# Solution: $V_{\text{UTP}} = \frac{R_2}{R_1 + R_2} \left( +V_{out(max)} \right) = \frac{10 \text{ k}\Omega}{47 \text{ k}\Omega + 10 \text{ k}\Omega} \left( +13 \text{ V} \right)$ = 2.28 V

By symmetry, the lower trigger point = -2.28 V.

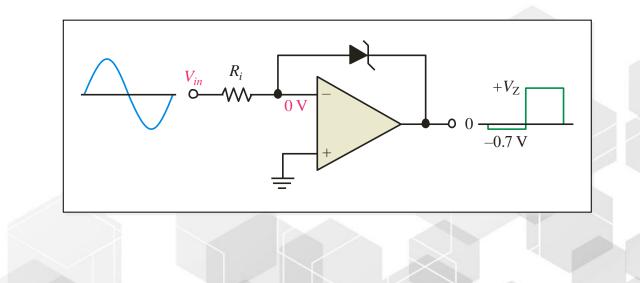

## **Output Bounding**

Some applications require a limit to the output of the comparator (such as a digital circuit). The output can be limited by using one or two Zener diodes in the feedback circuit.

The circuit shown here is bounded as a positive value equal to the zener breakdown voltage.

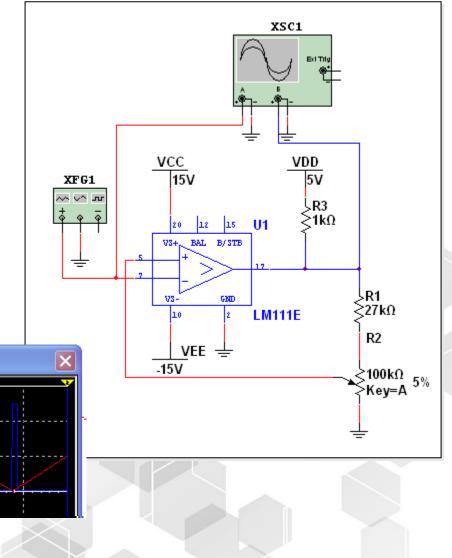

#### **Comparator Applications**

A comparator with hysteresis can produce a pulse with a variable duty cycle. For the circuit shown,  $V_{out(max)}$  ranges from 0 V to +5 V because of the GND and  $V_{DD}$  connections on the LM311.

The input is the red triangle wave (0 to 4 V). The duty cycle is varied with  $R_2$ .

Oscilloscope-XSC1

to 5%, a

With  $R_2$  set

short pulse is

the resúlt.

#### **Comparator Applications**

#### **Comparator Applications**

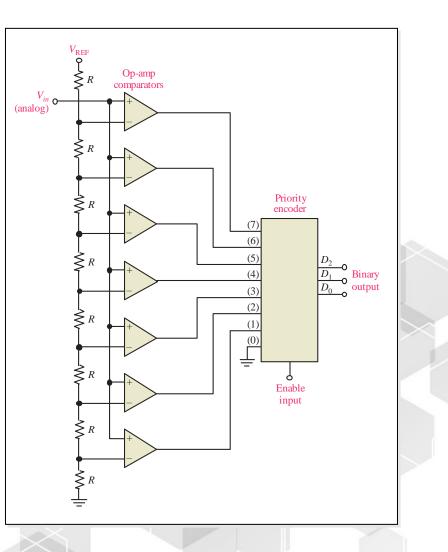

Simultaneous or flash analog-to-digital converters use 2<sup>n</sup>-1 comparators to convert an analog input to a digital value for processing. Flash ADCs are a series of comparators, each with a slightly different reference voltage. The priority encoder produces an output equal to the highest value input.

In IC flash converters, the priority encoder usually includes a latch that holds the converter data constant for a period of time after the conversion.

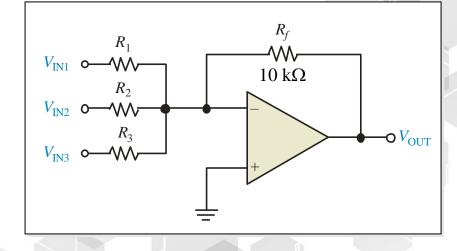

## **Summing Amplifier**

A **summing amplifier** has two or more inputs; normally all inputs have unity gain. The output is proportional to the negative of the algebraic sum of the inputs.

Example:

What is  $V_{OUT}$  if the input voltages are +5.0 V, -3.5 V and +4.2 V and all resistors = 10 k $\Omega$ ?

Solution:  $V_{OUT} = -(V_{IN1} + V_{IN2} + V_{IN3})$   $= -(+5.0 \vee - 3.5 \vee + 4.2 \vee)$  $= -5.7 \vee$

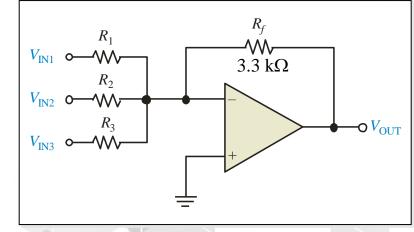

## **Averaging Amplifier**

An **averaging amplifier** is basically a summing amplifier with the gain set to  $R_f/R = 1/n$  (*n* is the number of inputs). The output is the negative average of the inputs.

Example:

What is  $V_{OUT}$  if the input voltages are +5.0 V, -3.5 V and +4.2 V? Assume  $R_1 = R_2 = R_3 = 10 \text{ k}\Omega$  and  $R_f = 3.3 \text{ k}\Omega$ ?

$V_{OUT} = -\frac{1}{3}(V_{IN1} + V_{IN2} + V_{IN3})$ = -\frac{1}{3}(+5.0 \text{ V} - 3.5 \text{ V} + 4.2 \text{ V}) = -1.9 \text{ V}

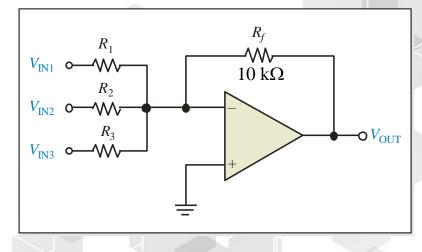

### **Scaling Adder**

A **scaling adder** has two or more inputs with each input having a different gain. The output represents the negative *scaled* sum of the inputs.

Assume you need to sum the inputs from three microphones. The first two microphones require a gain of -2, but the third microphone requires a gain of -3. What are the values of the input R's if  $R_f = 10 \text{ k} \Omega$ ?

# **Solution:** R<sub>c</sub>

$$R_{1} = R_{2} = -\frac{R_{f}}{A_{v1}} = -\frac{10 \text{ k}\Omega^{2}}{-2} = 5.0 \text{ k}\Omega$$

$$R_{3} = -\frac{R_{f}}{A_{v3}} = -\frac{10 \text{ k}\Omega}{-3} = 3.3 \text{ k}\Omega$$

10 kO

#### **Scaling Adder**

PHENIKAA UNIVERSITY

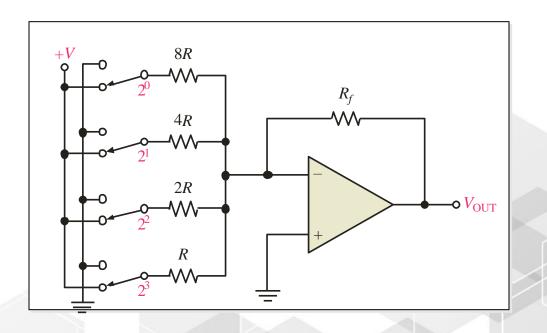

An application of a **scaling adder** is the D/A converter circuit shown here. The resistors are inversely proportional to the binary column weights. Because of the precision required of resistors, the method is useful only for small DACs.

#### http://phenikaa-uni.edu.vn

UNIVERSIT

A more widely used method for D/A conversion is the *R***/2***R* **ladder**. The gain for  $D_3$  is -1. Each successive input has a gain that is half of previous one. The output represents a weighted sum of all of the inputs (similar to the scaling adder).

$Q D_0$

R

$R_2$

2R

=

Inputs

$Q D_2$

$\leq \tilde{2R}$

$R_8$

R

O D

$\leq \frac{1}{2R}$

$R_f = 2R$

٨٨,

$-0V_{out}$

Q D

2R

R

An advantage of the *R/2R* ladder is that only two values of resistors are required to implement the circuit.

## **R/2R Ladder DAC**

#### **The Integrator**

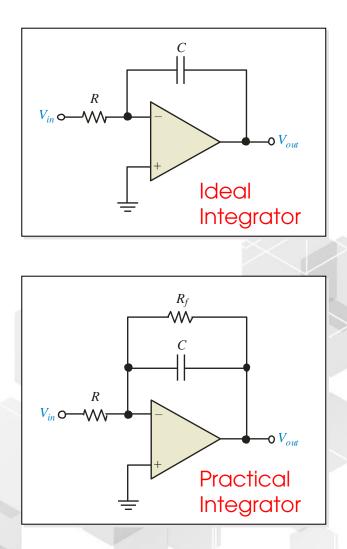

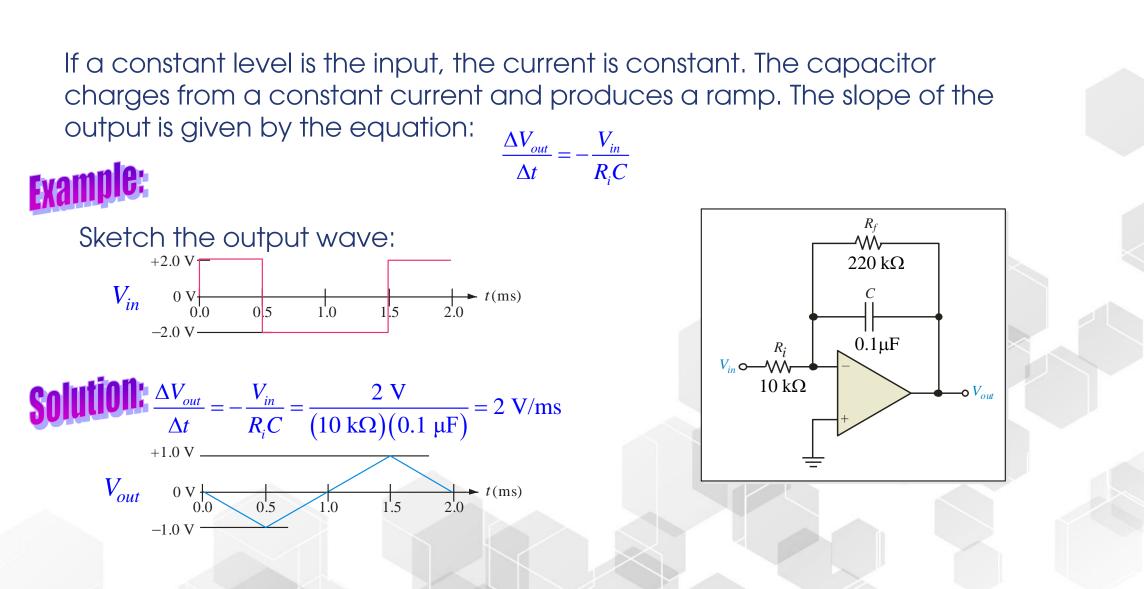

The **ideal integrator** is an inverting amplifier that has a capacitor in the feedback path. The output voltage is proportional to the negative integral (running sum) of the input voltage.

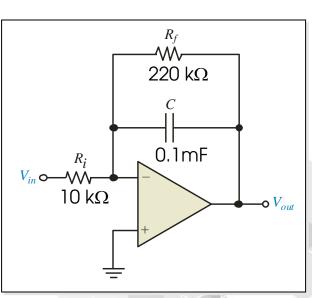

Op-amp integrating circuits must have extremely low dc offset and bias currents, because small errors are equivalent to a dc input. The ideal integrator tends to accumulate these errors, which moves the output toward saturation. The **practical integrator** overcomes these errors– the simplest method is to add a relatively large feedback resistor.

#### **The Integrator**

UNIVERSIT

#### **The Integrator**

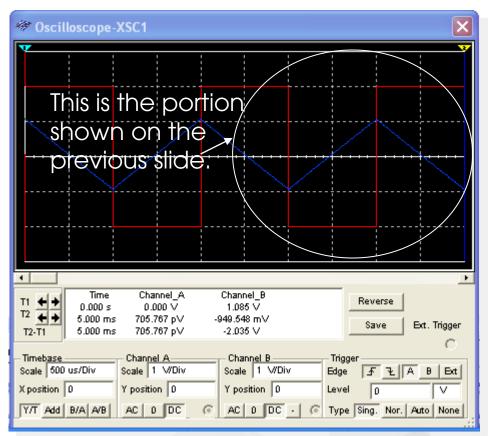

#### The result from the previous example can be confirmed with Multisim.

http://phenikaa-uni.edu.vn

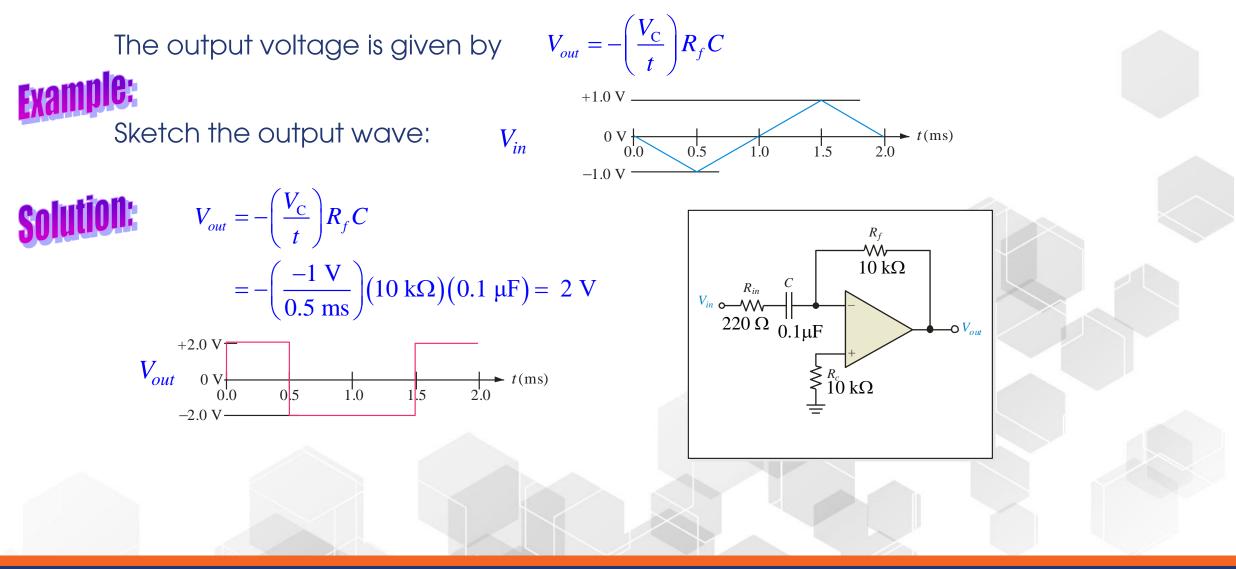

#### **The Differentiator**

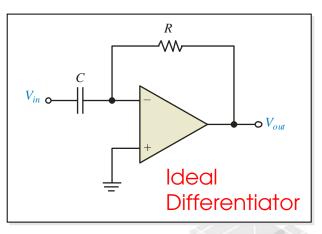

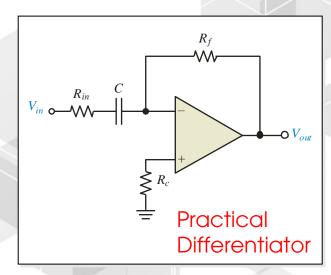

The **ideal differentiator** is an inverting amplifier that has a capacitor in the input path. The output voltage is proportional to the negative rate of change of the input voltage.

The small reactance of *C* at high frequencies means an ideal differentiator circuit has very high gain for high-frequency noise. To compensate for this, a small series resistor is often added to the input. This **practical differentiator** has reduced high frequency gain and is less prone to noise.

#### **The Differentiator**